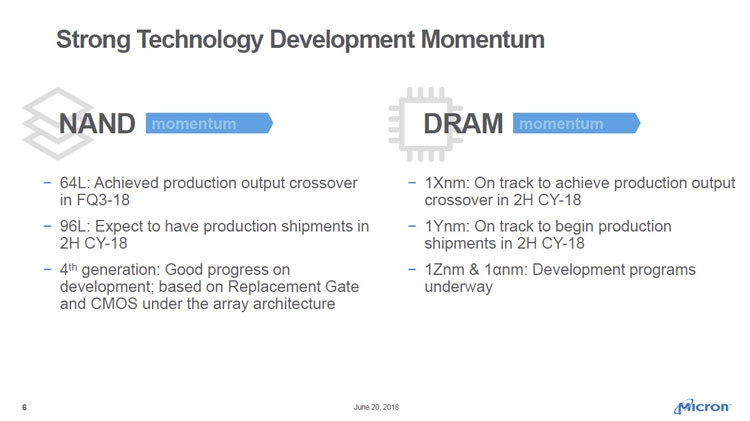

В преддверии симпозиума VLSI 2018 организация Micron Technology губами аккуратного президента Скотта ДеБоера (Scott DeBoer) открыла проекты по подготовке свежих техпроцессов изготовления памяти вида DRAM и 3D NAND. Начнём с материнской платы. Докладывается, что техпроцессы класса 10 hm пройдут 5 ступеней, 3 из которых ещё предстоит отчетливо спроектировать. На данный момент организация широко производит микросхемы DRAM с применением первой генерации техпроцесса класса 10 hm под кодовым названием 1Xnm (скорее всего — это 17 hm). В третьем полугодии объёмы изготовления чипов с общепризнанными мерками 1Xnm начнут превосходить объёмы изготовления DRAM класса 20 hm, равномерно вытесняя их из выражения.

Третье поколение техпроцесса класса 10 hm либо 1Ynm спроектировано, но произведенные благодаря ему микросхемы DRAM проходят искусные исследования у партнёканал Micron. Глобальный выпуск микросхем материнской платы с общепризнанными мерками 1Ynm начнется до конца 2016 года. Под кодовым названием 1Ynm может прятаться как 16-нм, так и 15-нм процесс. В Micron данной информации не открывают.

Третья генерация техпроцесса класса 10 hm либо 1Znm располагается в стадии разработки кристалла и в ходе проработки нужных производственных операций. Согласно слухам, это будут технические нормы значения 13 hm. 2-мя следующими техпроцессами Micron будут техпроцессы 1α (альфа) и 1β (бета). Оба они, как ясно даже из заглавий, располагаются на начальной ступени подготовки. Техпроцессы 1α и 1β также будут относиться к классу 10 hm, однако они могут спуститься ниже данной арифметической границы, впрочем Micron не стала заводить кодовое имя класса 0Xnm. Как и организация «Самсунг», Micron также будет применять в дальнейшем сканеры спектра EUV для изготовления памяти, однако начнёт это делать приблизительно с техпроцесса 1β.

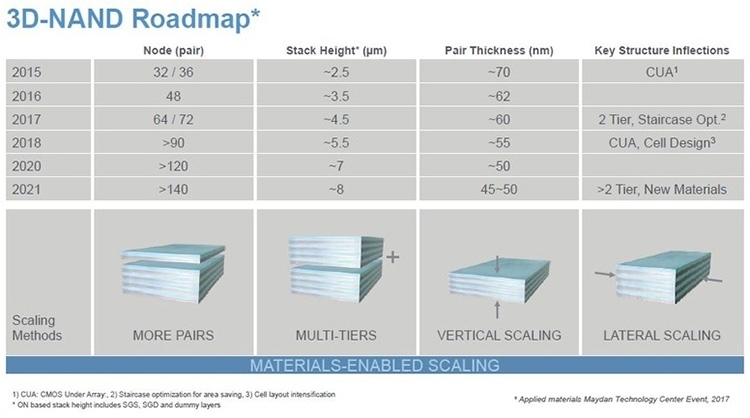

Многообещающие виды по наращиванию насыщенности 3D NAND

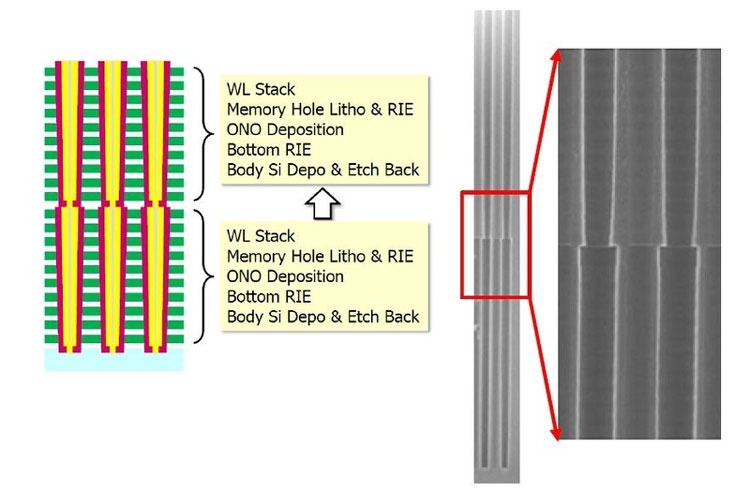

Что же касается двухслойной памяти NAND (3D NAND), то Micron обещала до конца календарного года приступить к изготовлению 96-слойных 512-Гбит чипов. Так как ёмкость чипов не повысится, кристаллы выйдут беспрецедентно небольшой для промышленности площади. В пересчёте на себестоимость кристаллов — это отличная весть. Ужасная весть состоит в том, что 96-слоёв нельзя сделать в одном кристалле и свежие чипсеты будут заключаться из 2-ух состыкованных вместе 48-слойных кристаллов.

96-слойная 3D NAND вполне может быть составлена из 2-ух 48-слойных кристаллов 3D NAND (International Memory Workshop 2018)

Тем не менее, организация Micron может создавать стеки из кристаллов 3D NAND. Если верить источникам, 64-слойная память 3D NAND производится как в качестве единого кристалла, так и в качестве стеков из 2-ух 32-слойных кристаллов. К слову, выпуск цельных 64-слойных кристаллов открывает маршрут к сравнительно обычному изготовлению четвёртого поколения 3D NAND в качестве 128-слойных микросхем.

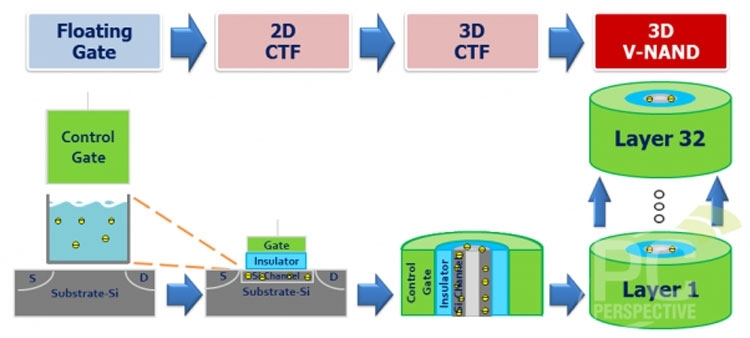

Память 3D NAND может применять различный вид ячей: с западнею заряда либо с плавучим затвором

Также Micron доказала, что в четвёртом поколении 3D NAND она откажется от ячеи NAND с плавучим затвором и перейдёт на ячейку NAND с западнею заряда. Как итог, пропускная дееспособность 3D NAND памяти компании повысится на 30 %, но употребление энергии в пересчёте на бит хранимых данных уменьшится на 40 %. Хорошо!

Сентябрь 16th, 2024

Сентябрь 16th, 2024  raven000

raven000  Опубликовано в рубрике

Опубликовано в рубрике