Как мы знаем, энергонезависимую память STT-MRAM (spin-transfer torque MRAM) сейчас производит организация GlobalFoundries по плану компании Everspin Технолоджис. Насыщенность 40-нм микросхем STT-MRAM составляет всего 256 Mbit (32 Мбайт), что рентабельно возмещается повышенной скоростью работы и большей стойкостью к уничтожению в процессе операций чистки, чем в случае памяти NAND. Эти большие качества STT-MRAM дают возможность претендовать магниторезистивной памяти с записью данных при помощи перевода спинового этапа (spin-transfer torque) на место в микропроцессоре. По меньшей мере речь идёт о смене массивов SRAM на массивы STT-MRAM в роли кеш-памяти 3-го значения (L3). Но что с кеш-памятью L1 и L2?

По словам экспертов бельгийского экспериментального центра Imec, для применения магниторезистивной памяти MRAM в роли энергонезависимого кеша первого и 2-го значений память STT-MRAM подходит не слишком хорошо. На данную роль претендует не менее идеальный вариант магниторезистивной памяти, а конкретнее — SOT-MRAM (spin-orbit torque MRAM). Запись в ячейку SOT-MRAM также происходит спин-поляризованным током, однако в виде передачи поворотного этапа, применяя для этого спин-орбитальный момент электронов.

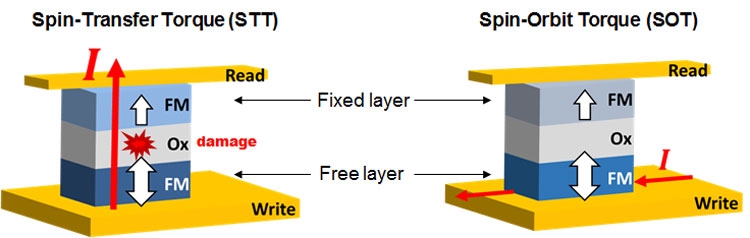

Серьезная разница состоит в схеме администрирования туннельным переходом в составе ячеи памяти и в способе записи. Так, клетка STT-MRAM представляет из себя бутерброд из 2-ух тонкоплёвечерних строений (разделённых диэлектриком), одна из которых имеет регулярную намагниченность, но 2-я «свободную» — подходящую от поляризации вложенного тока. Запись и прочтение данных из такой ячеи случаются одинаково при пропускании токов параллельно через тоннельный переход. Этим самым износ ячеи происходит как в процессе записи, так и в процессе чтения, впрочем при чтении флюиды существенно меньше, чем при записи.

Клетка с туннельным переходом SOT-MRAM, также имеющая свободный пласт и пласт с регулярной намагниченностью, вписывается током, который движется вдоль туннельного прохода, а не через все слои. Изменение «геометрии» подачи тока, говорят в Imec, существенно улучшает как стойкость ячеи к сносу, так и скорость переключения пласта. По сравнению работы ячей STT-MRAM и SOT-MRAM, произведенных на одинаковой пластинке типоразмера 300 миллиметров, для SOT-MRAM стойкость к сносу превзошла 5·1010, но скорость переключения ячеи (запись) уменьшилась с 5 нс до 210 пс (пикосекунд). Употребление при этом было на малом уровне, равном 300 пДж (пикоджоулей).

Особенный шарм всей данной истории состоит в том, что в Imec продемонстрировали вероятность производить память SOT-MRAM на стандартном оснащении на 300-мм кремниевых подложках. Иными словами, на утилитарном уровне установили вероятность старта глобального изготовления памяти вида SOT-MRAM.

Июль 14th, 2023

Июль 14th, 2023  raven000

raven000  Опубликовано в рубрике

Опубликовано в рубрике