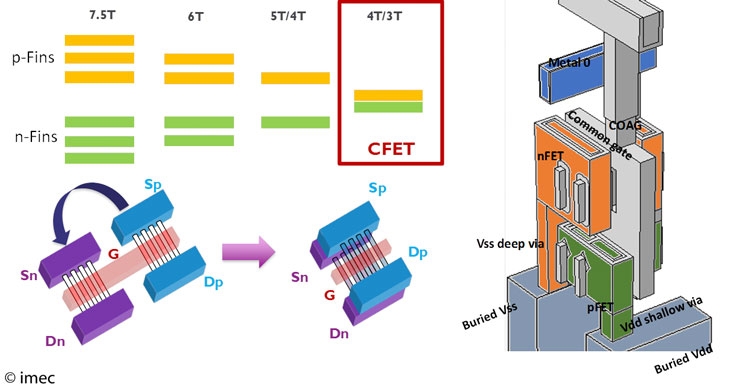

Imec продолжает радовать подготовками, открывающими маршрут к изготовлению полупроводников с общепризнанными мерками менее 5–3 hm. Среди других отчетов на симпозиуме VLSI Technology 2018 создатели центра сообщили о обнаруженной серии технических цепочек, которая позволит производить взаимодополняющие пары равнинных транзисторов с применением технических общепризнанных мерок менее 3 hm (complementary FET, CFET). Процесс изготовления CFET по энергоэффективности и мощности транзисторов может в конечном итоге опередить процесс FinFET согласно к техническим общепризнанным меркам 3 hm. И более того, процесс CFET открывает вероятность снизить на 50 % габариты как обычных (цифровых) ячей, так и ячей памяти SRAM.

Справа обозначены виды здания ячей (обычной и SRAM), но слева — представленная Imec лестная конструкция из 2-ух транзисторов

Напоминаем, что на применении взаимодополняющих пар транзисторов основывается традиционные КМОП (CMOS) техпроцессы изготовления микросхем. Это транзисторы с различным видом проводимости (n и p), однако схожие либо схожие по характеристикам. Создатели Imec вписали храброе предложение формировать на кристалле лестные транзисторы не рядом, но приятель над другом. В представленной Imec цепочке операций по обработке кремниевой пластинки полевой триод n-типа (nFET) находится над равнинным транзистором p-типа (pFET).

Триод pFET сделан в качестве отвесного ребра (практически FinFET), но триод nFET в качестве выкинутой над ним наностраницы (на самом деле аналогичного ребра FinFET). Особенная прелесть этой системы в том, что она создаётся в стандартном техпроцессе, как для производства транзисторов FinFET. Тест системы при помощи TCAD-инструментов подтверждает, что мощность и употребление CFET, произведенных с применением 3-нм техпроцесса, превзойдёт характеристики транзисторов FinFET в хорошую сторону. Все-таки, есть неприятность, с которой ещё придётся разобраться — это повышенное чужеядное противодействие отдела включения истока к высшему nFET-транзистору (происходит существенное снижение усилия Vss). Эту неприятность можно решить, к примеру, за счёт применения рутения в роли проводника.

Что же касается объема ячей, то «цифровую» либо обычную ячейку в случае CFET чунаётся сблизить к схеме с 3-мя серьезными рёбрами FinFET (3 контактных площадки в 1-м покрове металлизации), но ячейку SRAM — к схеме с 4-мя серьезными рёбрами FinFET. Передовые же техпроцессы позволяют формировать ячейку с 6 серьезными рёбрами и не меньше (6T). На иллюстрации выше, объясним, представлены лишь серьезные рёбра FinFET. Рёбра-пустышки, которые делят серьезные FinFET, не задействованы в схеме ячеи, на иллюстрации изменены пустейшими местами, однако на кристалле они на физическом уровне находятся и занимают место. «Трехэтажные» взаимодополняющие транзисторы позволят со смыслом применять окружающую площадь. В данном с Imec согласны партнёры по платформе подготовки компании GlobalFoundries, Huawei, Intel, Micron, Qualcomm, «Самсунг», SK Hynix, Сони Semiconductor Solutions, TOSHIBA Memory, TSMC и Western Диджитал.

Апрель 13th, 2024

Апрель 13th, 2024  raven000

raven000  Опубликовано в рубрике

Опубликовано в рубрике